(善)力疾走

西川善司のブログ

with the throttle against the stop...

「ATI Radeon HD 5800」徹底分析(3)~3Dグラフィックスに特化したAMD

RADEON HD5800シリーズのアーキテクチャ考察、最終回です。

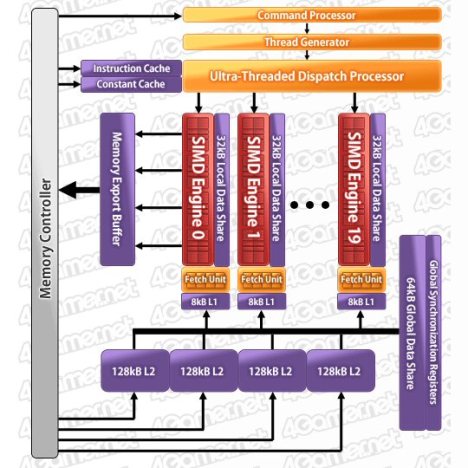

最終回ではレンダリングパイプライン後段周りについてのアーキテクチャ解説を行っています。

特に注目すべきは内部バスの伝送速度強化、そしてキャッシュシステムの大幅なリファインでしょうか。

例えばL1キャッシュシステムと演算コアを結ぶ内部バスはビット幅を倍にしています。(おそらく1024ビットバス)

ただし、RADEON HD5800シリーズは、基本的にRADEON HD4800シリーズの倍化アーキテクチャなので、倍増した演算コアを高効率に動かすために、そうしたリファインは必要不可欠だった…という見方が正しいとは思います。

西川善司の3Dゲームエクスタシー

「ATI Radeon HD 5800」徹底分析(3)~3Dグラフィックスに特化したAMD

http://www.4gamer.net/games/085/G008506/20091021037/

根本的に3Dグラフィックスプロセッサとしての素性を持つRADEON HD5800シリーズですが、GPGPU用途への対応を強化するために、バッファ類の容量倍化も積極的に行われています。

例えばRADEON HD 4800シリーズで「Shader Export Buffer」と呼ばれていたブロックは、RADEON HD 5800シリーズでは「Memory Export Buffer」と呼び名を変えていますが、ここの容量は2倍に増加されていますし、Local Data Shareは2倍、Global Data Shareは4倍に増加させられています。

これらLocal&Global Data Shareの強化はAMDのGPGPUへの意気込みの現れといったところでしょうか。

もちろん、これらの強化は3DグラフィックスレンダリングはDirectX11のテッセレーションステージの高効率化実行、DirectX10.xのジオメトリシェーダのパフォーマンス向上への計らいもあるのかもしれませんが。

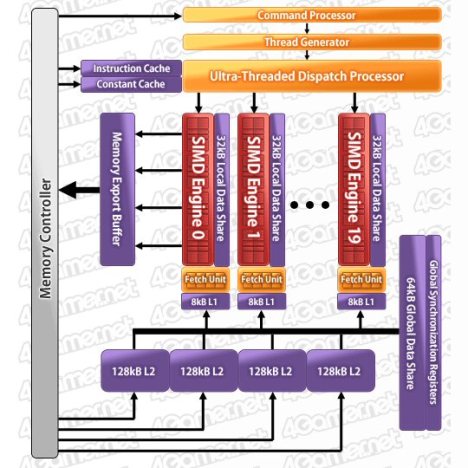

最終回ではレンダリングパイプライン後段周りについてのアーキテクチャ解説を行っています。

特に注目すべきは内部バスの伝送速度強化、そしてキャッシュシステムの大幅なリファインでしょうか。

例えばL1キャッシュシステムと演算コアを結ぶ内部バスはビット幅を倍にしています。(おそらく1024ビットバス)

ただし、RADEON HD5800シリーズは、基本的にRADEON HD4800シリーズの倍化アーキテクチャなので、倍増した演算コアを高効率に動かすために、そうしたリファインは必要不可欠だった…という見方が正しいとは思います。

西川善司の3Dゲームエクスタシー

「ATI Radeon HD 5800」徹底分析(3)~3Dグラフィックスに特化したAMD

http://www.4gamer.net/games/085/G008506/20091021037/

根本的に3Dグラフィックスプロセッサとしての素性を持つRADEON HD5800シリーズですが、GPGPU用途への対応を強化するために、バッファ類の容量倍化も積極的に行われています。

例えばRADEON HD 4800シリーズで「Shader Export Buffer」と呼ばれていたブロックは、RADEON HD 5800シリーズでは「Memory Export Buffer」と呼び名を変えていますが、ここの容量は2倍に増加されていますし、Local Data Shareは2倍、Global Data Shareは4倍に増加させられています。

これらLocal&Global Data Shareの強化はAMDのGPGPUへの意気込みの現れといったところでしょうか。

もちろん、これらの強化は3DグラフィックスレンダリングはDirectX11のテッセレーションステージの高効率化実行、DirectX10.xのジオメトリシェーダのパフォーマンス向上への計らいもあるのかもしれませんが。

Trackbacks

Trackback URL : http://www.z-z-z.jp/BLOG/sb.cgi/466

Comments